Vending machine control

Prerequisites: Study the functionality of Vending machine control.

Learning Objective: To develop the source code for Vending machine control by using VERILOG and obtain the simulation and synthesis.

Software and Hardware: Xilinx ISE 9.2i and FPGA Spartan-3E.

Theory:

Verilog Code:

module vending (

input clk,

input rst,

input [1:0] coin,

output [1:0] gd

);

localparam IDLE = 3'b000;

localparam RE1 = 3'b001;

localparam RS2 = 3'b010;

localparam SUCC = 3'b011;

localparam FAIL = 3'b100;

reg [2:0] state_reg, state_next;

always @(posedge clk, posedge rst) begin

if(rst)

state_reg <= IDLE;

else

state_reg <= state_next;

end

always @* begin

case(state_reg)

IDLE: begin

case(coin)

2'b00: state_next = IDLE;

2'b01: state_next = RE1;

2'b10: state_next = RS2;

2'b11: state_next = FAIL;

default: state_next = IDLE;

endcase

end

RE1: begin

case(coin)

2'b00: state_next = RE1;

2'b01: state_next = RS2;

2'b10: state_next = SUCC;

2'b11: state_next = FAIL;

default: state_next = IDLE;

endcase

end

RS2: begin

case(coin)

2'b00: state_next = RS2;

2'b01: state_next = SUCC;

2'b10: state_next = FAIL;

2'b11: state_next = FAIL;

default: state_next = IDLE;

endcase

end

SUCC: begin

case(coin)

2'b00: state_next = IDLE;

2'b01: state_next = RE1;

2'b10: state_next = RS2;

2'b11: state_next = FAIL;

default: state_next = IDLE;

endcase

end

FAIL: begin

case(coin)

2'b00: state_next = IDLE;

2'b01: state_next = FAIL;

2'b10: state_next = FAIL;

2'b11: state_next = FAIL;

default: state_next = IDLE;

endcase

end

default: state_next = IDLE;

endcase

end

assign gd[1] = (state_reg == SUCC);

assign gd[0] = (state_reg == FAIL);

endmodule

TEST BENCH:

module tb_vending;

// inputs

reg clk;

reg rst;

reg [1:0] coin;

// outputs

wire [1:0] gd;

vending DUT (.clk(clk), .rst(rst), .coin(coin), .gd(gd));

initial begin

clk = 0;

rst = 0;

coin = 0;

end

initial forever #10 clk = ~clk;

initial begin

#5;

@(negedge clk) rst = ~rst;

@(negedge clk) rst = ~rst;

end

initial begin

#60;

@(negedge clk) coin =2'b00 ;

@(negedge clk) coin =2'b01 ;

@(negedge clk) coin =2'b01 ;

@(negedge clk) coin =2'b01 ;

@(negedge clk) coin =2'b00 ;

@(negedge clk) coin =2'b10 ;

@(negedge clk) coin =2'b01 ;

@(negedge clk) coin =2'b00 ;

@(negedge clk) coin =2'b10 ;

@(negedge clk) coin =2'b10 ;

@(negedge clk) coin =2'b11 ;

@(negedge clk) coin =2'b10 ;

@(negedge clk) coin =2'b00 ;

@(negedge clk) coin =2'b00 ;

@(negedge clk) coin =2'b10 ;

@(negedge clk) coin =2'b01 ;

end

endmodule

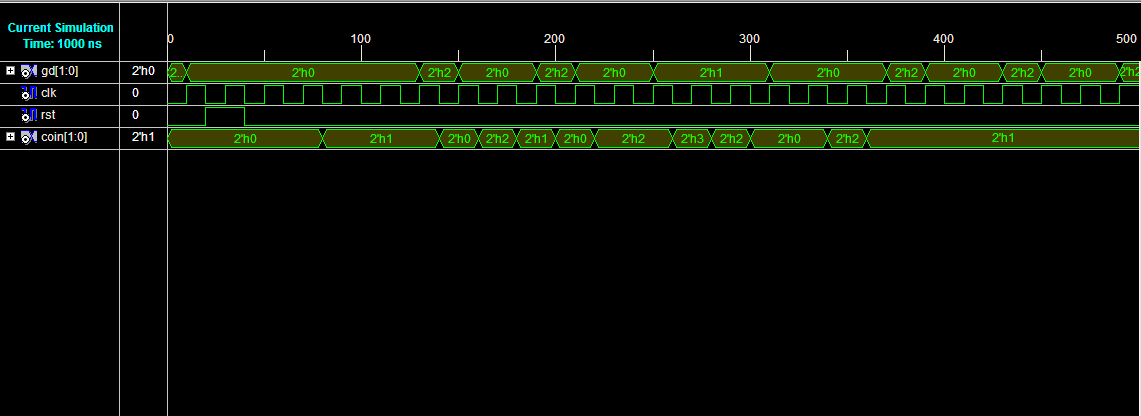

SIMULATION RESULTS:

Result: Thus the program for vending machine has been verified and also simulation and synthesis reports have been verified.

Outcomes: After completion of this experiment students are able to design vending machine using Verilog code.

-

UpdatedOct 15, 2016

-

Views3,355