HDL code 4-to-2 Priority Encoder

Prerequisites: Study the functionality of Priority Encoder.

Learning Objective: To develop the source code for 4 to 2 line priority encoder by using VERILOG and obtain the simulation and synthesis.

Software and Hardware: Xilinx ISE 9.2i and FPGA Spartan-3E.

Theory:

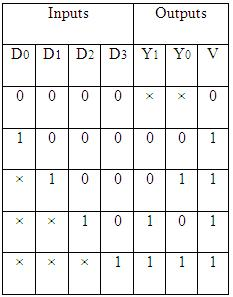

A priority encoder is a circuit or algorithm that compresses multiple binary inputs into a smaller number of outputs. The output of a priority encoder is the binary representation of the ordinal number starting from zero of the most significant input bit. They are often used to control interrupt requests by acting on the highest priority request. It includes priority function. If two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence. Internal hardware will check this condition and priority is set.

Table: Truth Table of 4 bit priority encoder

Figure: Logic Diagram of 4 bit priority encoder

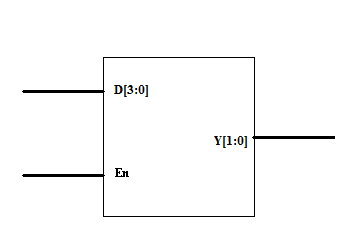

Block Diagram:

Verilog Code:

module priorityencoder(Y, Din, En);

input [3:0] D;

input En;

output [1:0]Y;

reg [1:0]Eo;

always @ ( En or Din)

begin

if (En)

begin

casex (Din)

4'b0001: Eo = 2'b00;

4'b001x: Eo = 2'b01;

4'b01xx: Eo = 2'b10;

4'b1xxx: Eo = 2'b11;

default: $display("Error!");

endcase

end

end

endmodule

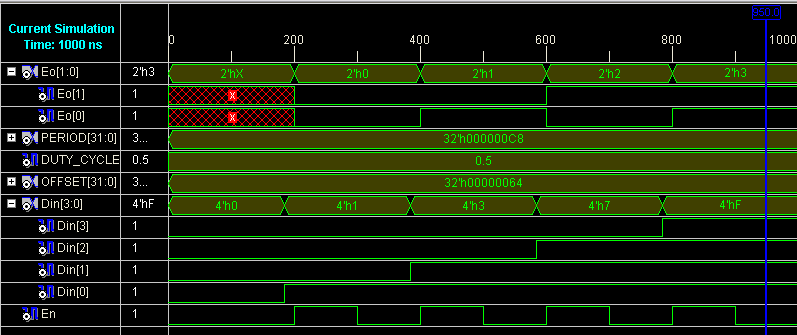

Simulation Results:

Result: Designed and verified the functionality of Priority encoder.

Learning outcome: After completion of this experiment, students are able to design Priority encoder using Verilog.

Viva Questions:

- What does Priority encoder mean?

- What are the applications of Priority encoder?

- What is the difference between encoder and Priority encoder?

- Name the digital IC Number that is used as Priority encoder?

-

UpdatedOct 30, 2016

-

Views17,034