Finite State Machine (Mealy Machine)

Prerequisites: Study the functionality of Mealy Machine.

Learning Objective: To develop the source code for Melay machine by using VERILOG and obtain the simulation and synthesis.

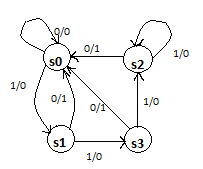

Meay Machine

Software and Hardware: Xilinx ISE 9.2i and FPGA Spartan-3E.

Theory: The output of a Moore finite state machine depends only on the machine's current state; transitions are not directly dependent upon input.

- The use of a Mealy FSM leads often to a reduction of the number of states.

| Present State | Next State | Output | ||

|---|---|---|---|---|

| X = 0 | X = 1 | X = 0 | X = 1 | |

| S0 | S0 | S1 | 0 | 0 |

| S1 | S0 | S3 | 1 | 0 |

| S2 | S0 | S2 | 1 | 0 |

| S3 | S0 | S2 | 1 | 0 |

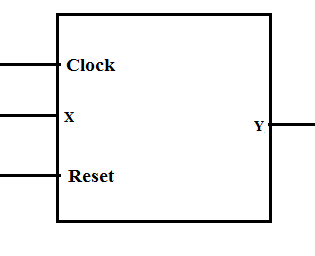

Block Diagram:

Verilog Code:

module FSM_Mealy( y, x, clock, reset);

input x, clock, reset;

output y;

reg y;

reg [1:0] Prstate, Next_state;

parameter s0 = 2'b00, s1 = 2'b01, s2 = 2'b10, s3 = 2'b11;

always @(posedge clock)

begin

if (reset)

Prstate = s0;

else

Prstate = Next_state;

end

always @(Prstate or x)

begin

case (Prstate)

s0: if (x)

begin

Next_state = s1;

y = 1'b0;

end

else

begin

Next_state = s0;

y = 1'b0;

end

s1: if (x)

begin

Next_state = s3;

y = 1'b0;

end

else

begin

Next_state = s0;

y = 1'b1;

end

s2: if (~x)

begin

Next_state = s0;

y = 1'b1;

end

else

begin

Next_state = s2;

y = 1'b0;

end

s3: if (x)

begin

Next_state = s2;

y = 1'b0;

end

else

begin

Next_state = s0;

y = 1'b1;

end

endcase

end

endmodule

TEST BENCH:

module FSM_Mealy_tb_v;

reg x;

reg clock;

reg reset;

wire y;

FSM_Mealy uut(

.y(y),

.x(x),

.clock(clock),

.reset(reset)

);

initial begin

x = 0; clock = 0; reset = 1;

#10 x = 0; reset = 0;

#10 x = 1;

#10 x = 0;

#10 x = 1;

#10 x = 1;

#10 x = 0; #100;

end

always #5 clock = ~clock;

endmodule

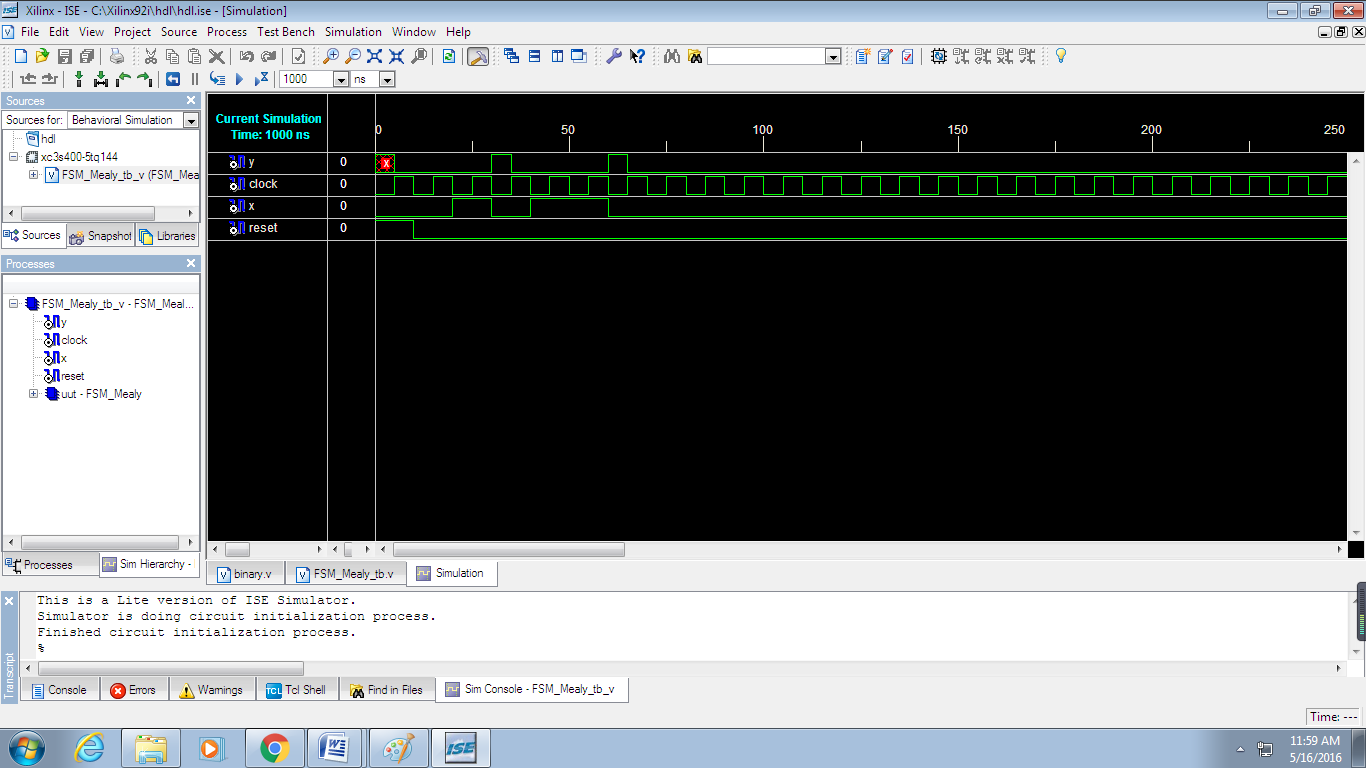

Simulation Results:

Result: Thus the program for Mealy FSM has been verified and also simulation and synthesis reports have been verified.

Learning outcome: After completion of this experiment, students are able to design Mealy machine using Verilog code.

Viva Questions:

- What is the function of Mealy machine?

- What is the difference between blocking and non blocking statement?

- What is the difference between ‘always’ and ’initial’ statements?

- What is the difference between ‘case x’ and ‘case z’?

-

UpdatedNov 21, 2021

-

Views5,259